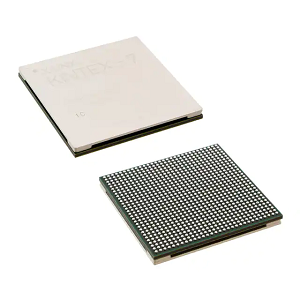

XC7K420T-2FFG901I – Nā Kaapuni i hoʻohui ʻia, Hoʻokomo ʻia, Nā ʻīpuka ʻīpuka Programmable kahua.

Huahana Huahana

| ANO | HOIKE |

| waeʻano | Nā Kaapuni Hoʻohui (IC)Hoʻokomo ʻia Nā ʻīpuka puka pā papahana (FPGA) |

| mea hana | AMD |

| moʻo | Kintex®-7 |

| kāʻei | pā |

| Kūlana huahana | ʻeleu |

| Hiki ke hoʻolālā ʻia ʻo DigiKey | ʻAʻole hōʻoia |

| Helu LAB/CLB | 32575 |

| Ka helu o nā mea hoʻonaʻauao / ʻāpana | 416960 |

| Huina helu o ka RAM bits | 30781440 |

| Ka helu o I/Os | 380 |

| Voltage - lako mana | 0.97V ~ 1.03V |

| ʻAno hoʻokomo | ʻAno hoʻopili i luna |

| Hana wela | -40°C ~ 100°C (TJ) |

| Pūʻolo/Hāle | 900-BBGA, FCBGA |

| Hoʻopili ʻāpana mea kūʻai aku | 901-FCBGA (31x31) |

| Helu haku huahana | XC7K420 |

| ANO | HOIKE |

| waeʻano | Nā Kaapuni Hoʻohui (IC)Hoʻokomo ʻia |

| mea hana | AMD |

| moʻo | Kintex®-7 |

| kāʻei | pā |

| Kūlana huahana | ʻeleu |

| Hiki ke hoʻolālā ʻia ʻo DigiKey | ʻAʻole hōʻoia |

| Helu LAB/CLB | 32575 |

| Ka helu o nā mea hoʻonaʻauao / ʻāpana | 416960 |

| Huina helu o ka RAM bits | 30781440 |

| Ka helu o I/Os | 380 |

| Voltage - lako mana | 0.97V ~ 1.03V |

| ʻAno hoʻokomo | ʻAno hoʻopili i luna |

| Hana wela | -40°C ~ 100°C (TJ) |

| Pūʻolo/Hāle | 900-BBGA, FCBGA |

| Hoʻopili ʻāpana mea kūʻai aku | 901-FCBGA (31x31) |

| Helu haku huahana | XC7K420 |

Nā FPGA

Nā pono

ʻO nā pono o nā FPGA penei:

(1) Loaʻa nā FPGA i nā kumuwaiwai lako e like me nā cell logic, RAM, multipliers, a me nā mea ʻē aʻe.

(2) Hiki ke hoʻolālā ʻia nā FPGA ma o ka hoʻohana ʻana i nā kiʻi poloka a i ʻole Verilog HDL, mai nā kaʻa ʻīpuka maʻalahi a i nā kaapuni FIR a i ʻole FFT.

(3) Hiki ke hoʻonohonoho hou ʻia nā FPGA, e hoʻouka ana i kahi hoʻolālā hoʻolālā hou i loko o nā haneli milliseconds wale nō, me ka hoʻohana ʻana i ka hoʻonohonoho hou ʻana e hōʻemi i ka ʻoihana ma luna.

(4) Hoʻoholo ʻia ke alapine hana o ka FPGA e ka puʻupuʻu FPGA a me ka hoʻolālā ʻana, a hiki ke hoʻololi a hoʻololi ʻia me kahi chip wikiwiki e hoʻokō i kekahi mau koi koi (ʻoiai, ʻoiaʻiʻo, ʻaʻole palena ʻole ka alapine hana. e hoʻonui ʻia, akā mālama ʻia e nā kaʻina hana IC o kēia manawa a me nā mea ʻē aʻe).

Nā pōʻino

ʻO nā hemahema o nā FPGA penei:

(1) Ke hilinaʻi nei nā FPGA i ka hoʻokō ʻana i ka ʻenehana no nā hana āpau a ʻaʻole hiki ke hoʻokō i nā hana e like me ka lele kūlana lālā.

(2) Hiki i nā FPGA ke hoʻokō i nā hana paʻa.

I ka hōʻuluʻulu manaʻo: Ke hilinaʻi nei nā FPGA i nā lako hana e hoʻokō i nā hana āpau a hiki ke hoʻohālikelike ʻia me nā chips i hoʻolaʻa ʻia ma ke ʻano o ka wikiwiki, akā aia kahi ākea nui i ka hoʻolālā hoʻolālā e hoʻohālikelike ʻia me nā mea hana maʻamau.

Nā ʻōlelo hoʻolālā a me nā paepae

ʻO nā polokalamu logic programmable nā mea lawe lako e hoʻopaʻa i nā hana i hoʻokumu ʻia a me nā kikoʻī ʻenehana o nā noi uila ma o ka ʻenehana EDA.ʻO nā FPGA, ʻo ia kekahi o nā mea hana nui e hoʻokō nei i kēia ala, he mea hoʻohana pololei, maʻalahi a maʻalahi, maʻalahi e hoʻohana, a wikiwiki hoʻi e hoʻāʻo a hoʻokō i nā lako.

ʻO ka ʻōlelo wehewehe ʻo Hardware (HDL) he ʻōlelo i hoʻohana ʻia no ka hoʻolālā ʻana i nā ʻōnaehana loiloi kikohoʻe a wehewehe i nā kaapuni kikohoʻe, ʻo nā mea nui i hoʻohana mau ʻia ʻo VHDL, Verilog HDL, System Verilog a me System C.

Ma ke ʻano he ʻōlelo wehewehe lako lako holoʻokoʻa, loaʻa i ka Very High Speed Integrated Circuit Hardware Description Language (VHDL) nā hiʻohiʻona o ke kūʻokoʻa ʻana i ke kaʻapuni ʻenehana kikoʻī a kūʻokoʻa i ke kahua hoʻolālā, me nā pono o ka hiki ke wehewehe ākea, ʻaʻole hilinaʻi i nā mea kiko'ī, a me ka hiki ke wehewehe i ka hoʻolālā ʻana i ka manaʻo hoʻokele paʻakikī i kahi code paʻakikī a pōkole, etc. Ua kākoʻo ʻia e nā hui EDA he nui a ua hoʻohana nui ʻia ma ke kahua o ka hoʻolālā uila.hoʻohana nui ʻia.

He ʻōlelo kūlana kiʻekiʻe ʻo VHDL no ka hoʻolālā kaapuni, a ke hoʻohālikelike ʻia me nā ʻōlelo wehewehe ʻenehana ʻē aʻe, loaʻa iā ia nā hiʻohiʻona o ka ʻōlelo maʻalahi, ka maʻalahi a me ke kūʻokoʻa mai ka hoʻolālā ʻana o ka mea hana, e lilo ia i ʻōlelo wehewehe ʻenehana maʻamau no ka ʻenehana EDA a me ka hoʻonui ʻana i ka ʻenehana EDA. hiki i nā mea hoʻolālā.

ʻO Verilog HDL kahi ʻōlelo wehewehe ʻenehana i hiki ke hoʻohana ʻia i nā pae he nui o ke kaʻina hana hoʻolālā, me ka hoʻohālike, synthesis a me ka simulation.

Nā Pono o Verilog HDL: like me C, maʻalahi ke aʻo a maʻalahi.Hoʻopaʻa hiʻohiʻona.Nā pōmaikaʻi ma ke kākau ʻana i ka hoʻoulu ʻana a me ka hoʻohālike.Nā hemahema: ʻaʻole hiki ke ʻike ʻia nā hewa he nui i ka manawa hōʻuluʻulu.

Nā Pono VHDL: Syntax koʻikoʻi, ka hierarchy maopopo.Nā pōʻino: lōʻihi ka manawa familiarization, ʻaʻole lawa ka maʻalahi.

ʻO ka polokalamu Quartus_II kahi hoʻolālā hoʻolālā multi-platform piha i hoʻomohala ʻia e Altera, hiki ke hoʻokō i nā pono hoʻolālā o nā FPGA like ʻole a me nā CPLD, a he wahi ākea no ka hoʻolālā ʻōnaehana programmable on-chip.

ʻO Vivado Design Suite, kahi hoʻolālā i hoʻohui ʻia i hoʻokuʻu ʻia e ka mea kūʻai aku ʻo FPGA Xilinx ma 2012. Loaʻa iā ia kahi hoʻolālā hoʻolālā hoʻohui nui a me kahi hanauna hou o nā mea hana mai ka ʻōnaehana a hiki i ka pae IC, nā mea a pau i kūkulu ʻia ma ke ʻano hoʻohālike data scalable a me kahi kaiapuni debug maʻamau.Hāʻawi ka Xilinx Vivado Design Suite i nā koina FIFO IP hiki ke hoʻohana maʻalahi i nā hoʻolālā.