XC7A75T2FGG484I

Huahana Huahana

| ANO | HOIKE | |

| waeʻano | Nā Kaapuni Hoʻohui (IC) | |

| mea hana | AMD | |

| moʻo | Artix-7 | |

| kāʻei | pā | |

| Kūlana huahana | ʻeleu | |

| Hiki ke hoʻolālā ʻia ʻo DigiKey | ʻAʻole hōʻoia | |

| Helu LAB/CLB | 5900 |

|

| Ka helu o nā mea hoʻonaʻauao / ʻāpana | 75520 |

|

| Huina helu o ka RAM bits | 3870720 |

|

| I/O 數 | 285 |

|

| Voltage - lako mana | 0.95V~1.05V |

|

| ʻAno hoʻokomo | ʻAno hoʻopili i luna |

|

| Hana wela | -40°C ~ 100°C(TJ) |

|

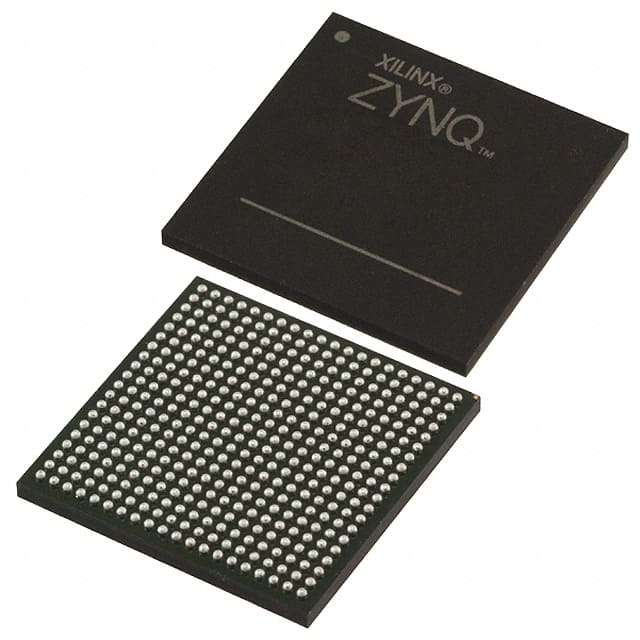

| Pūʻolo/Hāle | 484-BBGA |

|

| Hoʻopili ʻāpana mea kūʻai aku | 484-FBGA (23x23) |

|

| Helu haku huahana | XC7A75 |

Hoʻolauna Huahana

ʻO Artix-7 FPGA DC a me AC nā hiʻohiʻona i hōʻike ʻia i ka pāʻoihana, lōʻihi, ʻoihana, hoʻonui (-1Q), a me ka pūʻali koa (-1M).Ma waho aʻe o ka pae wela o ka hana ʻana a inā ʻaʻole i ʻike ʻia, ua like nā ʻāpana uila DC a me AC no kahi māka wikiwiki (ʻo ia hoʻi, ʻo nā ʻano manawa o kahi mea kaua wikiwiki -1M e like me ka -1C wikiwiki. mea kalepa).Eia naʻe, loaʻa nā māka wikiwiki a/a i ʻole nā mea hana i kēlā me kēia pae wela.No ka laʻana, loaʻa ka -1M i ka ʻohana Artix-7Q pale-pale a loaʻa -1Q i nā XA Artix-7 FPGA wale nō.

ka noi o FPGA

1. kahua kamaʻilio.

Pono ke kahua o ke kamaʻilio ʻana i ka hana protocol kamaʻilio kiʻekiʻe.Ma ka ʻaoʻao ʻē aʻe, ke hoʻololi ʻia nei ka protocol kamaʻilio i kēlā me kēia manawa, ʻaʻole kūpono ia no ka hana ʻana i kahi chip kūikawā.No laila, ua lilo ka FPGA me nā hana maʻalahi i koho mua.

Ke hoʻohana nui nei ka ʻoihana kelepona i nā FPGA.Ke hoʻololi mau nei nā kūlana kelepona a paʻakikī loa ke kūkulu ʻana i nā lako kelepona, no laila, ʻo nā hui e hāʻawi ana i nā ʻōnaehana kelepona e hopu mua i ka māhele mākeke nui loa.No ka lōʻihi o ka hana ʻana o nā ASIC, hāʻawi nā FPGA i kahi manawa no kahi pōkole.Ua hoʻomaka nā mana mua o nā lako kelepona e hoʻohana i nā FPGA, kahi i alakaʻi ai i nā hakakā kumukūʻai FPGA.ʻOiai ʻaʻole pili ke kumukūʻai o FPGA i ka mākeke emulation ASIC, ʻo ke kumu kūʻai o nā ʻāpana telecom.

2. Māhele algorithm.

Hiki iā FPGA ke hana i nā hōʻailona paʻakikī a hiki ke mālama i nā hōʻailona multi-dimensional.

3. kahua hoʻokomo.

Ke hoʻohana nei i ka FPGA e kūkulu i kahi kaiapuni i hoʻopili ʻia, a laila kākau i kekahi polokalamu i hoʻopili ʻia ma luna ona, ʻoi aku ka paʻakikī o nā hana transactional, a ʻoi aku ka liʻiliʻi o nā hana ma FPGA.

4. Ma ke kahua o ka nānā ʻana i ka palekana

I kēia manawa, paʻakikī i ka CPU ke hoʻokō i ka hana multi-channel a me ka ʻike a me ka nānā wale ʻana, akā hiki ke maʻalahi ma hope o ka hoʻohui ʻana i ka FPGA, ʻoi aku hoʻi i ke kahua o nā algorithms kiʻi, nona nā pono kūʻokoʻa.

5. Ma ke kahua o ka automation ʻoihana

Hiki i ka FPGA ke hoʻokō i ka mana kaʻa kaʻa he nui.I kēia manawa, ʻo ka hoʻohana ʻana i ka mana kaʻa ka hapa nui o ka ikehu honua.Ma lalo o ke ʻano o ka mālama ʻana i ka ikehu a me ka mālama ʻana i ke kaiapuni, e hoʻohana ʻia nā ʻano like ʻole o nā motika mana pololei i ka wā e hiki mai ana, a hiki i kahi FPGA hoʻokahi ke hoʻomalu i ka nui o nā kaʻa.

.jpg)